My research 🔎

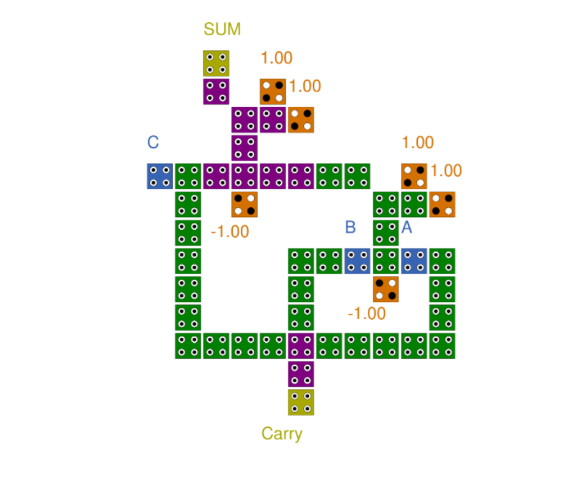

This paper presents a QCA full adder design using two 2-input XOR gates and a majority gate, achieving a

16.95% reduction in cell count, a 22.22% improvement in the cost function, and lower latency.

Simulations confirm its efficiency, reliability, and suitability for advanced digital systems like

microprocessors.

Devised a prediction algorithm using deep learning to estimate willingness of the inactive users in a

VAA cell. Achieved 35% faster discovery time with an impressive 98.2% accuracy. Also used a

cryptographic algorithm to ensure reliability ans security in industrial IOT networks.